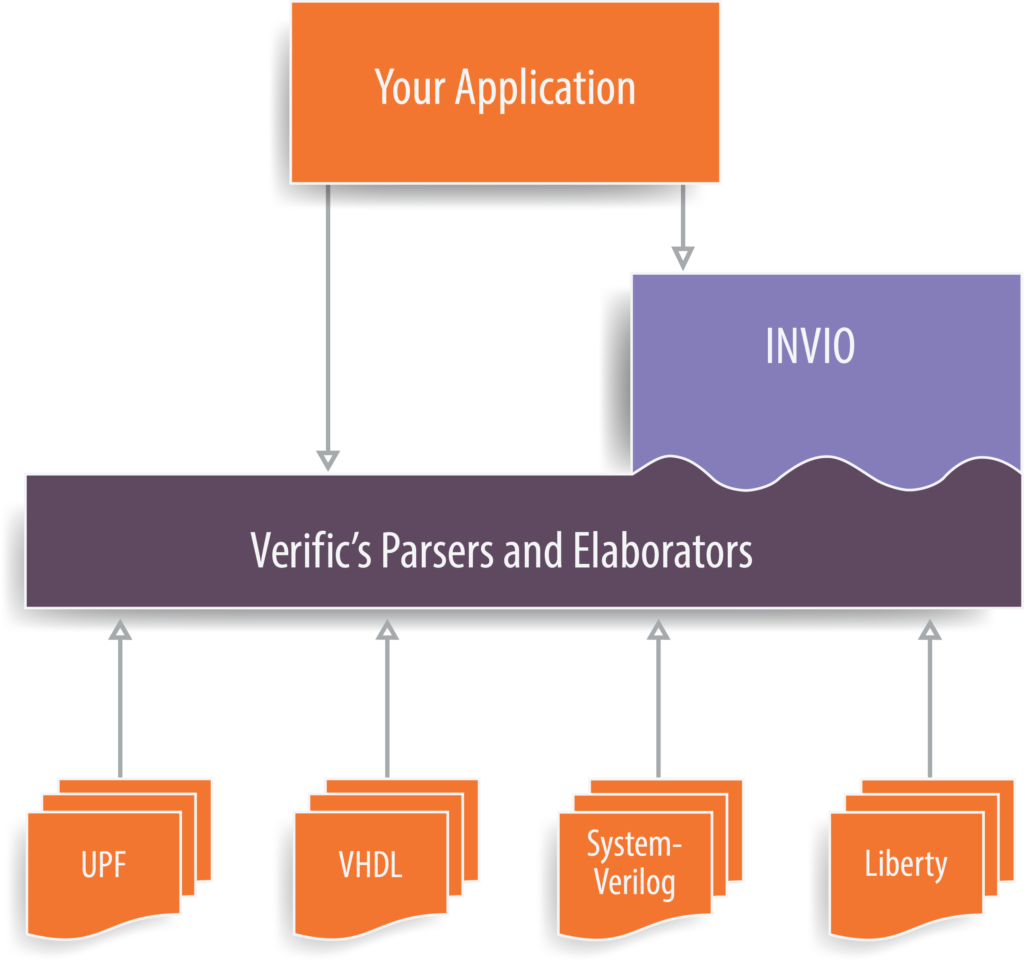

The INVIO platform is meant for CAD, design, and verification engineers. INVIO is an easy to learn Python API built on top of Verific’s SystemVerilog, UPF, and VHDL platforms. It also provides a suite of application specific plug-in examples for RTL modification, functional verification, netlist modification, and SoC assembly.

INVIO objects can be directly referenced by connectivity to other objects at the HDL level, allowing very quick and natural navigation of designs and test benches. All INVIO objects (instances, signals, processes, etc.) can be referenced by their full hierarchical names and all instance names are fully resolved, enabling a more natural design view. An intuitive ‘regex’ search on all attributes is included. All references (signals, classes, interfaces, etc.) are fully resolved by INVIO, enabling simple automatic support for complex SystemVerilog including hierarchical references, classes, virtual functions, and UVM. INVIO supports user attributes and automatically enables powerful search on new user attributes.

The INVIO in-place modification API enables development of tools that modify existing RTL designs while preserving the look and feel of the original text file (indentation, comments, whitespace, etc.).

Do you want more information?

Try our Free 30-day Evaluation Package, our downloads page or just contact us.