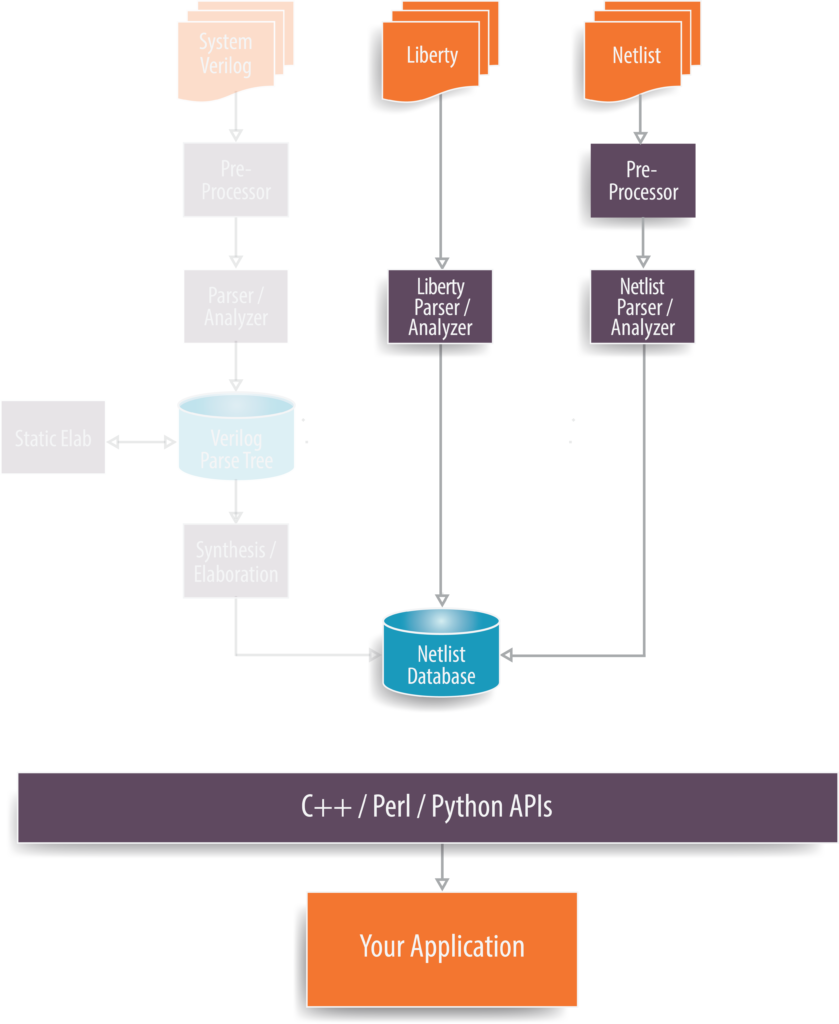

Verific’s Verilog Netlist Only Parser reads a Verilog structural netlist directly into Verific’s hierarchical database. It does not create any intermediate parse tree or other persistent data structure.

The Verilog Netlist Only Parser can be of great use to EDA applications that do not (yet) require RTL support.

As with all Verific’s software, the product is shipped as C++ source code and backed with a rigorous support and maintenance program.

Netlist Database

- Average memory usage approximately 300 bytes / instance

- Full hierarchy support, with grouping/ungrouping, etc.

- Find, insert, remove, and change cells, ports, and wires.

- Full support for any number of libraries, and no restrictions on library interaction (instantiations across different libraries).

- Maintains all attribute information

- Support for busses.

- Compact storage of line and file origination.

- Comprehensive error handler.

- Simple and clean data model and Procedural Interface

Do you want more information?

Try our Free 30-day Evaluation Package, our downloads page or just contact us.